- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

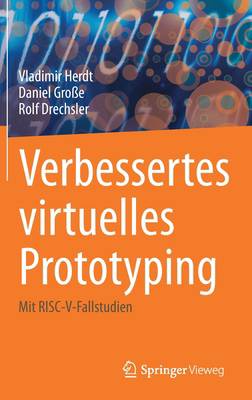

Verbessertes Virtuelles Prototyping

Mit Risc-V-Fallstudien

Vladimir Herdt, Daniel Große, Rolf DrechslerOmschrijving

Dieses Buch stellt eine umfassende Reihe von Techniken vor, die alle wichtigen Aspekte eines modernen Virtual Prototype (VP)-basierten Entwurfsablaufs verbessern. Die Autoren legen den Schwerpunkt auf automatisierte formale Verifikationsmethoden sowie auf fortgeschrittene, abdeckungsgeleitete Analyse- und Testtechniken, die auf SystemC-basierte VP und die zugehörige Software (SW) zugeschnitten sind. Die Abdeckung umfasst auch VP-Modellierungstechniken, die sowohl funktionale als auch nicht-funktionale Aspekte behandeln, und beschreibt zudem Korrespondenzanalysen zwischen der Hardware- und VP-Ebene, um die auf verschiedenen Abstraktionsebenen verfügbaren Informationen zu nutzen. Alle Ansätze werden ausführlich diskutiert und anhand mehrerer Experimente evaluiert, um ihre Effektivität bei der Verbesserung des VP-basierten Entwurfsablaufs zu demonstrieren. Darüber hinaus legt das Buch einen besonderen Schwerpunkt auf den modernen RISC-V ISA, mit mehreren Fallstudien, die sowohl Aspekteder Modellierung als auch der VP- und SW-Verifikation abdecken.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 262

- Taal:

- Duits

Eigenschappen

- Productcode (EAN):

- 9783031181733

- Verschijningsdatum:

- 2/01/2023

- Uitvoering:

- Hardcover

- Formaat:

- Genaaid

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 580 g

Alleen bij Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.