- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

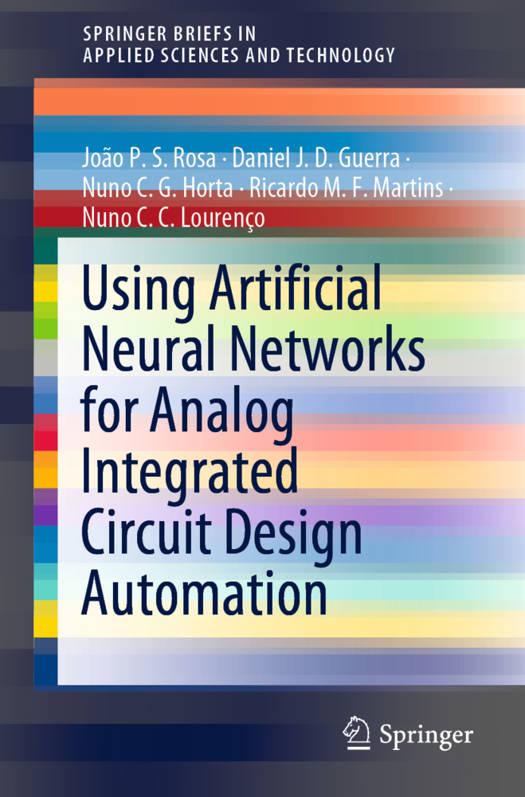

Using Artificial Neural Networks for Analog Integrated Circuit Design Automation

João P S Rosa, Daniel J D Guerra, Nuno C G Horta, Ricardo M F Martins, Nuno C C Lourenço

€ 68,95

+ 137 punten

Omschrijving

This book addresses the automatic sizing and layout of analog integrated circuits (ICs) using deep learning (DL) and artificial neural networks (ANN). It explores an innovative approach to automatic circuit sizing where ANNs learn patterns from previously optimized design solutions. In opposition to classical optimization-based sizing strategies, where computational intelligence techniques are used to iterate over the map from devices' sizes to circuits' performances provided by design equations or circuit simulations, ANNs are shown to be capable of solving analog IC sizing as a direct map from specifications to the devices' sizes. Two separate ANN architectures are proposed: a Regression-only model and a Classification and Regression model. The goal of the Regression-only model is to learn design patterns from the studied circuits, using circuit's performances as input features and devices' sizes as target outputs. This model can size a circuit given its specifications for a single topology. The Classification and Regression model has the same capabilities of the previous model, but it can also select the most appropriate circuit topology and its respective sizing given the target specification. The proposed methodology was implemented and tested on two analog circuit topologies.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 101

- Taal:

- Engels

- Reeks:

Eigenschappen

- Productcode (EAN):

- 9783030357429

- Verschijningsdatum:

- 2/01/2020

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 176 g

Alleen bij Standaard Boekhandel

+ 137 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.