Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- In januari gratis thuislevering in België

- Ruim aanbod met 7 miljoen producten

Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- In januari gratis thuislevering in België

- Ruim aanbod met 7 miljoen producten

Zoeken

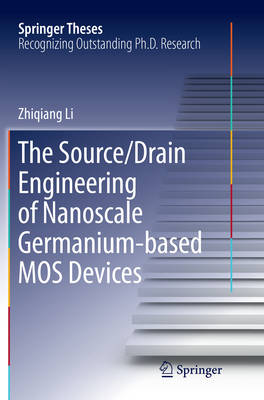

The Source/Drain Engineering of Nanoscale Germanium-based MOS Devices

Zhiqiang Li

€ 83,95

+ 167 punten

Uitvoering

Omschrijving

This book mainly focuses on reducing the high parasitic resistance in the source/drain of germanium nMOSFET. With adopting of the Implantation After Germanide (IAG) technique, P and Sb co-implantation technique and Multiple Implantation and Multiple Annealing (MIMA) technique, the electron Schottky barrier height of NiGe/Ge contact is modulated to 0.1eV, the thermal stability of NiGe is improved to 600 and the contact resistivity of metal/n-Ge contact is drastically reduced to 3.8×10-7 -cm2, respectively. Besides, a reduced source/drain parasitic resistance is demonstrated in the fabricated Ge nMOSFET. Readers will find useful information about the source/drain engineering technique for high-performance CMOS devices at future technology node.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 59

- Taal:

- Engels

- Reeks:

Eigenschappen

- Productcode (EAN):

- 9783662570265

- Verschijningsdatum:

- 7/06/2018

- Uitvoering:

- Paperback

- Afmetingen:

- 155 mm x 4 mm

- Gewicht:

- 151 g

Alleen bij Standaard Boekhandel

+ 167 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.