- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

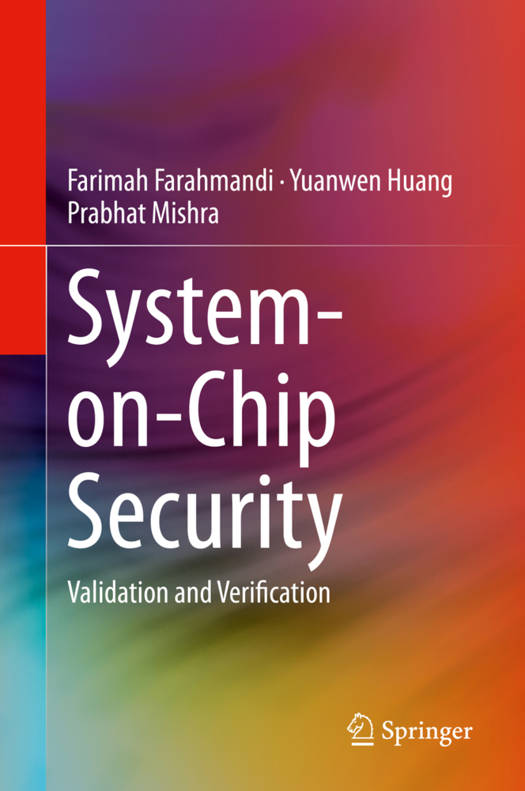

System-On-Chip Security

Validation and Verification

Farimah Farahmandi, Yuanwen Huang, Prabhat Mishra

Hardcover | Engels

€ 116,45

+ 232 punten

Uitvoering

Omschrijving

This book describes a wide variety of System-on-Chip (SoC) security threats and vulnerabilities, as well as their sources, in each stage of a design life cycle. The authors discuss a wide variety of state-of-the-art security verification and validation approaches such as formal methods and side-channel analysis, as well as simulation-based security and trust validation approaches. This book provides a comprehensive reference for system on chip designers and verification and validation engineers interested in verifying security and trust of heterogeneous SoCs.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 289

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783030305956

- Verschijningsdatum:

- 9/12/2019

- Uitvoering:

- Hardcover

- Formaat:

- Genaaid

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 612 g

Alleen bij Standaard Boekhandel

+ 232 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.