Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

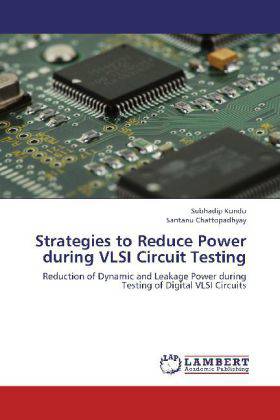

Strategies to Reduce Power during VLSI Circuit Testing

Reduction of Dynamic and Leakage Power during Testing of Digital VLSI Circuits

Subhadip Kundu, Santanu Chattopadhyay

Paperback | Engels

€ 48,45

+ 96 punten

Omschrijving

Testing is now considered as one of the most important issues in the development process of integrated circuits. With the advent of deep sub-micron (DSM) technology, the tight constraints on power dissipation have created new challenges for testing low power VLSI circuits. This necessitates redesigning the traditional test techniques that do not account for power dissipation during test application. Test power is always expected to be higher than that in the normal mode of operation of a circuit. High test power may lead to permanent or temporal damage of the chip. The objective of this thesis is to develop strategies to reduce test power consumption, considering both dynamic and leakage power, without compromising the fault coverage and thus increasing the manufacturing yield. Four different strategies (three for external testing and one for internal testing) have been developed in such a way that they require either zero or very small overhead in terms of area. The techniques also have no impact on fault coverage and functional critical path

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 116

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783659255205

- Uitvoering:

- Paperback

- Afmetingen:

- 150 mm x 220 mm

Alleen bij Standaard Boekhandel

+ 96 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.