Door een staking bij bpost kan je online bestelling op dit moment iets langer onderweg zijn dan voorzien. Dringend iets nodig? Onze winkels ontvangen jou met open armen!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Door een staking bij bpost kan je online bestelling op dit moment iets langer onderweg zijn dan voorzien. Dringend iets nodig? Onze winkels ontvangen jou met open armen!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

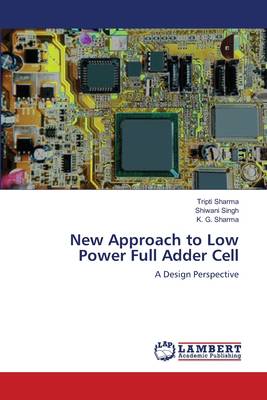

New Approach to Low Power Full Adder Cell

A Design Perspective

Tripti Sharma, Shiwani Singh, K G Sharma

Paperback | Engels

€ 48,45

+ 96 punten

Omschrijving

In recent years, low power design has become one of the prime focuses for digital VLSI circuits. As technology scales down, leakage currents in contemporary CMOS logic have become one of the main power consumers. Contrary to conventional methods for power reduction, operation of digital circuits in the subthreshold region minimizes power consumption in low-frequency systems. This book is based on pre-layout and post-layout simulations of a modified 9T full adder and 9T full adder circuit in subthreshold as well as super threshold region. The 9T circuit consists of a new logic, which is used to implement Sum module. This design remarkably reduces power consumption hence improves power-delay product (PDP) and temperature sustainability along with noise immunity and threshold loss when compared with the modified 8T adder. This book, therefore, provides a new metric of implementing high performance full adder circuit. This analysis should help shed some light on the new and exciting approach for achieving low power and high throughput adder cell and should be especially useful to post graduate students and research scholars in VLSI circuit design field.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 84

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783659137679

- Verschijningsdatum:

- 24/05/2012

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 152 mm x 229 mm

- Gewicht:

- 136 g

Alleen bij Standaard Boekhandel

+ 96 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.