Je cadeautjes zeker op tijd in huis hebben voor de feestdagen? Kom langs in onze winkels en vind het perfecte geschenk!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Je cadeautjes zeker op tijd in huis hebben voor de feestdagen? Kom langs in onze winkels en vind het perfecte geschenk!

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

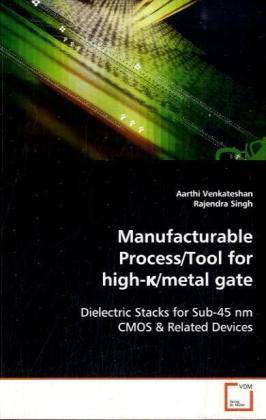

Manufacturable Process/Tool for high-κ/metal gate

Dielectric Stacks for Sub-45 nm CMOS

Aarthi Venkateshan, Rajendra Singh

Paperback | Engels

€ 115,95

+ 231 punten

Omschrijving

Off state leakage current related power dominates the CMOS heat dissipation problem of state of the art silicon integrated circuits. In this study, this issue has been addressed in terms of a low-cost single wafer processing (SWP) technique using a single tool for the fabrication of high-κ dielectric gate stacks for sub-45 nm CMOS. A system for monolayer photoassisted deposition was modified to deposit high-quality HfO2 films with in-situ clean, in-situ oxide film deposition, and in-situ anneal capability. The system was automated with Labview 8.2 for gas/precursor delivery, substrate temperature and UV lamp. The gold-hafnium oxide-aluminum (Au-HfO2-Al) stacks processed in this system had superior quality oxide characteristics with gate leakage current density on the order of 1 x 10-12 A/cm2 @ 1V and maximum capacitance on the order of 75 nF for EOT=0.39 nm. Achieving low leakage current density along with high capacitance demonstrated the excellent performance of the process developed. Detailed study of the deposition characteristics such as linearity, saturation behavior, film thickness and temperature dependence was performed for tight control on process parameters. Using Box-Behnken design of experiments, process optimization was performed for an optimal recipe for HfO2 films. UV treatment with in-situ processing of metal/high-κ dielectric stacks was studied to provide reduced variation in gate leakage current and capacitance. High-resolution transmission electron microscopy (TEM) was performed to calculate the equivalent oxide thickness (EOT) and dielectric constant of the films. Overall, this study shows that the in-situ fabrication of MIS gate stacks allows for lower processing costs, high throughput, and superior device performance.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 204

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783836481564

- Verschijningsdatum:

- 6/11/2008

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 152 mm x 229 mm

- Gewicht:

- 281 g

Alleen bij Standaard Boekhandel

+ 231 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.