Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Bedankt voor het vertrouwen het afgelopen jaar! Om jou te bedanken bieden we GRATIS verzending (in België) aan op alles gedurende de hele maand januari.

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

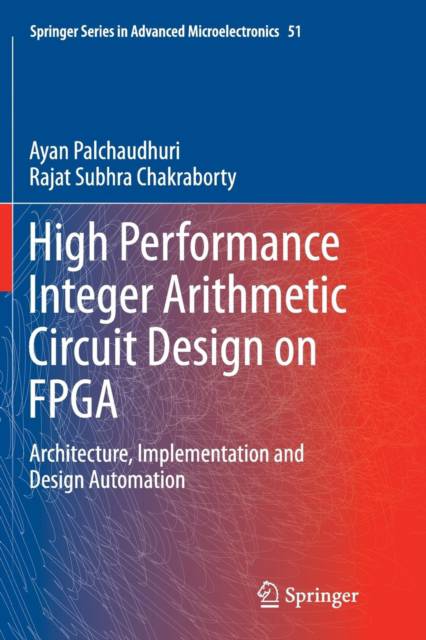

High Performance Integer Arithmetic Circuit Design on FPGA

Architecture, Implementation and Design Automation

Ayan Palchaudhuri, Rajat Subhra Chakraborty

€ 167,95

+ 335 punten

Uitvoering

Omschrijving

This book describes the optimized implementations of several arithmetic datapath, controlpath and pseudorandom sequence generator circuits for realization of high performance arithmetic circuits targeted towards a specific family of the high-end Field Programmable Gate Arrays (FPGAs). It explores regular, modular, cascadable and bit-sliced architectures of these circuits, by directly instantiating the target FPGA-specific primitives in the HDL. Every proposed architecture is justified with detailed mathematical analyses. Simultaneously, constrained placement of the circuit building blocks is performed, by placing the logically related hardware primitives in close proximity to one another by supplying relevant placement constraints in the Xilinx proprietary "User Constraints File". The book covers the implementation of a GUI-based CAD tool named FlexiCore integrated with the Xilinx Integrated Software Environment (ISE) for design automation of platform-specific high-performance arithmetic circuits from user-level specifications. This tool has been used to implement the proposed circuits, as well as hardware implementations of integer arithmetic algorithms where several of the proposed circuits are used as building blocks. Implementation results demonstrate higher performance and superior operand-width scalability for the proposed circuits, with respect to implementations derived through other existing approaches. This book will prove useful to researchers, students and professionals engaged in the domain of FPGA circuit optimization and implementation.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 114

- Taal:

- Engels

- Reeks:

- Reeksnummer:

- nr. 51

Eigenschappen

- Productcode (EAN):

- 9788132234357

- Verschijningsdatum:

- 23/10/2016

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 199 g

Alleen bij Standaard Boekhandel

+ 335 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.