- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

€ 105,45

+ 210 punten

Uitvoering

Omschrijving

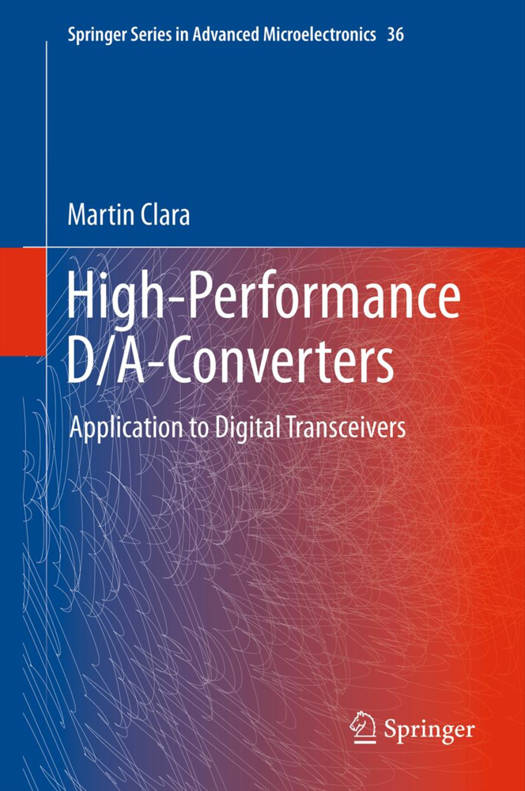

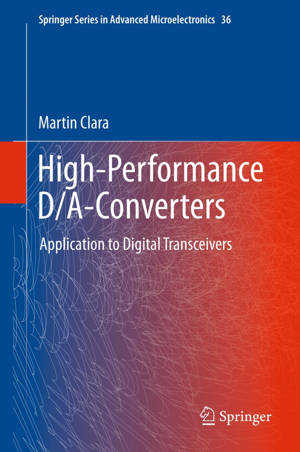

This book deals with modeling and implementation of high performance, current-steering D/A-converters for digital transceivers in nanometer CMOS technology. In the first part, the fundamental performance limitations of current-steering DACs are discussed. Based on simplified models, closed-form expressions for a number of basic non-ideal effects are derived and tested. With the knowledge of basic performance limits, the converter and system architecture can be optimized in an early design phase, trading off circuit complexity, silicon area and power dissipation for static and dynamic performance. The second part describes four different current-steering DAC designs in standard 130 nm CMOS. The converters have a resolution in the range of 12-14 bits for an analog bandwidth between 2.2 MHz and 50 MHz and sampling rates from 100 MHz to 350 MHz. Dynamic-Element-Matching (DEM) and advanced dynamic current calibration techniques are employed to minimize the required silicon area.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 286

- Taal:

- Engels

- Reeks:

- Reeksnummer:

- nr. 36

Eigenschappen

- Productcode (EAN):

- 9783642312281

- Verschijningsdatum:

- 22/12/2012

- Uitvoering:

- Hardcover

- Formaat:

- Genaaid

- Afmetingen:

- 155 mm x 231 mm

- Gewicht:

- 566 g

Alleen bij Standaard Boekhandel

+ 210 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.