- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

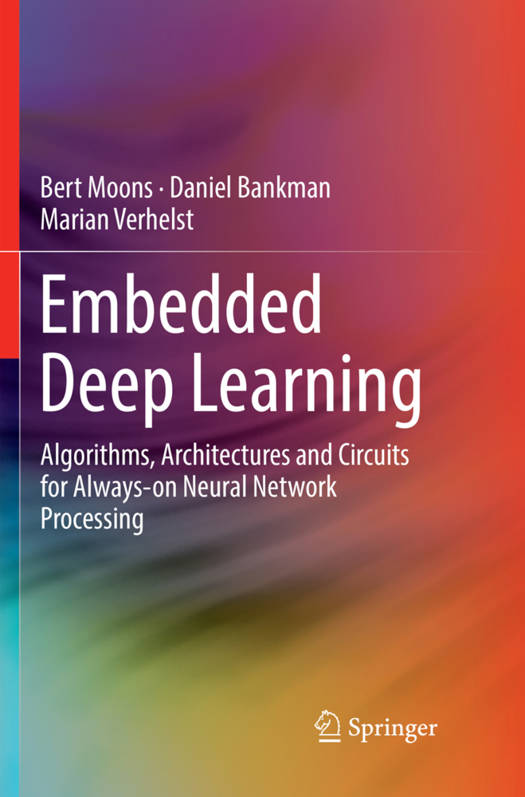

Embedded Deep Learning

Algorithms, Architectures and Circuits for Always-On Neural Network Processing

Bert Moons, Daniel Bankman, Marian Verhelst

Paperback | Engels

€ 94,95

+ 189 punten

Uitvoering

Omschrijving

This book covers algorithmic and hardware implementation techniques to enable embedded deep learning. The authors describe synergetic design approaches on the application-, algorithmic-, computer architecture-, and circuit-level that will help in achieving the goal of reducing the computational cost of deep learning algorithms. The impact of these techniques is displayed in four silicon prototypes for embedded deep learning.

- Gives a wide overview of a series of effective solutions for energy-efficient neural networks on battery constrained wearable devices;

- Discusses the optimization of neural networks for embedded deployment on all levels of the design hierarchy - applications, algorithms, hardware architectures, and circuits - supported by real silicon prototypes;

- Elaborates on how to design efficient Convolutional Neural Network processors, exploiting parallelism and data-reuse, sparse operations, and low-precision computations;

- Supports the introduced theory and design concepts by four real silicon prototypes. The physical realization's implementation and achieved performances are discussed elaborately to illustrated and highlight the introduced cross-layer design concepts.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 206

- Taal:

- Engels

Eigenschappen

- Productcode (EAN):

- 9783030075774

- Verschijningsdatum:

- 19/01/2019

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 317 g

Alleen bij Standaard Boekhandel

+ 189 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.