- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

- Afhalen na 1 uur in een winkel met voorraad

- Gratis thuislevering in België vanaf € 30

- Ruim aanbod met 7 miljoen producten

Zoeken

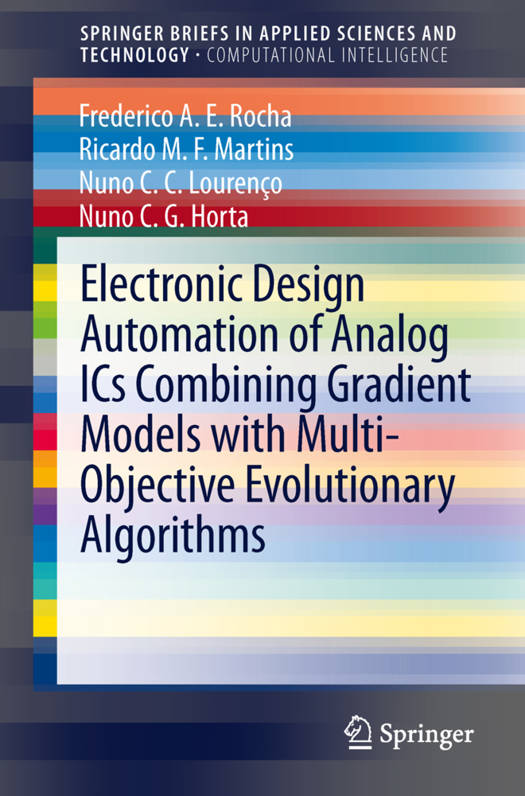

Electronic Design Automation of Analog ICS Combining Gradient Models with Multi-Objective Evolutionary Algorithms

Frederico a E Rocha, Ricardo M F Martins, Nuno C C Lourenço, Nuno C G Horta

Paperback | Engels | SpringerBriefs in Applied Sciences and Technology | SpringerBriefs in Computational Intelligence

€ 52,95

+ 105 punten

Omschrijving

This book applies to the scientific area of electronic design automation (EDA) and addresses the automatic sizing of analog integrated circuits (ICs). Particularly, this book presents an approach to enhance a state-of-the-art layout-aware circuit-level optimizer (GENOM-POF), by embedding statistical knowledge from an automatically generated gradient model into the multi-objective multi-constraint optimization kernel based on the NSGA-II algorithm. The results showed allow the designer to explore the different trade-offs of the solution space, both through the achieved device sizes, or the respective layout solutions.

Specificaties

Betrokkenen

- Auteur(s):

- Uitgeverij:

Inhoud

- Aantal bladzijden:

- 69

- Taal:

- Engels

- Reeks:

Eigenschappen

- Productcode (EAN):

- 9783319021881

- Verschijningsdatum:

- 15/10/2013

- Uitvoering:

- Paperback

- Formaat:

- Trade paperback (VS)

- Afmetingen:

- 156 mm x 234 mm

- Gewicht:

- 131 g

Alleen bij Standaard Boekhandel

+ 105 punten op je klantenkaart van Standaard Boekhandel

Beoordelingen

We publiceren alleen reviews die voldoen aan de voorwaarden voor reviews. Bekijk onze voorwaarden voor reviews.